Pioneer

SCALE-SIM 뜯어보기 (1): 설치 및 테스트 본문

SCALE-SIM이 뭔가요?

SCALE-SIM은 Systolic CNN AcceLErator SIMulator의 약자이다.

쉽게 말해, CNN 연산을 가속하기 위해 Systolic array를 사용하는 것을 시뮬레이션 해볼 수 있는 도구다.

그럼 그 다음 질문으로,

Systolic Array는 뭔데요?

Systolic의 사전적 의미는 "<생리> 심장 수축의"이라고 하는데, 심장 박동이라고 생각하는 것이 편하다.

왜 그런 이름이 붙었나? 아래 그림에서 자홍색 유닛 내의 데이터가 사이클에 따라 인접한 유닛으로 퍼져나가기 때문.

그리고 인접 유닛으로 퍼져나가는 점이 SRAM read bandwidth 절약과 데이터 재사용에 도움이 된다.

여기까지 찾아와주신 분이라면 아마 이것 보다 더 많은 것을 이미 알고 계시리라 생각한다.

혹여나 SCALE-SIM의 자세한 내용이 궁금하다면 아래 논문 2개를 읽어보고,

- Samajdar, A., et al., "Scale-sim cnn accelerator simulator," arXiv:1811.02883, '18

- Samajdar, A., et al., "A systematic methodology for characterizing scalability of DNN accelerators using SCALE-sim," ISPASS, '20

Systolic Array가 궁금하다면 구글과 유튜브에 Systolic Array를 검색해 석학들의 설명을 들어보자.

내가 이 오픈 소스를 뜯어 보려는 이유는 이걸 변형해서 무언가를 만들고 싶기 때문이다.

즉, 응용을 하고 싶은데 이를 위해선 완전한 이해가 선행돼야 한다.

시리즈의 첫 시작이므로 (설치 → 테스트 코드 실행 → 결과 확인) 정도의 간단한 작업만 수행해보자.

1. 설치

리눅스 기반 운영체제(e.g. Ubuntu)와 파이썬을 준비할 것

설치 방법엔 pip를 사용하는 방법과 리포지토리를 내려 받아 직접 설치하는 방법이 있다.

향후 소스 코드를 분석할거기 때문에, 후자를 선택.

git clone https://github.com/scalesim-project/scale-sim-v2.git

cd scale-sim-v2

python setup.py install

Finished processing dependencies for scalesim==2.0.2가 마지막에 뜬다면 성공

더 없냐고? 그렇다. 다른 오픈 소스들과 다르게 간단해서 좋다.

2. 테스트 코드 실행

실행 전, 필요한 것이 있다. 2개의 파일과 1개의 디렉터리다.

위 2개는 입력에, 마지막 하나는 결과 저장에 쓰인다.

- config_file: 시스템 아키텍처 정의 파일

- topology_file: DNN 구조 정의 파일, csv 포맷

- output_log_dir: 결과 저장 디렉터리

두 개의 파일은 직접 정의해도 되지만, 테스트용으로 제공되는게 몇 개 있다.

설정 파일로 configs/google.cfg와 토폴로지 파일로 topologies/conv_nets/alexnet.csv를 사용한다.

python scalesim/scale.py -c configs/google.cfg -t topologies/conv_nets/alexnet.csv -p outputs

리포지토리의 루트 위치에서 다음 커맨드를 입력하면 테스트가 시작된다.

outputs은 테스트 결과를 저장하기 위해 임의로 생성한 디렉터리다.

이렇게 시작해서,

레이어 단위로 수행되고,

마지막으로 "SCALE SIM Run Complete"가 나오면 끝난다.

3. 결과 확인

이제 outputs로 이동해서 결과 로그를 확인해보자.

2. 에서 나온 명령어를 실행하면 outputs에 GoogleTPU_v1_ws라는 이름의 디렉터리가 생성되었을 것이다.

그 이름으로 생성된 이유는 config_file 안의 [general] 아래 run_name에 그렇게 지정되었기 때문이다.

돌아와서,

해당 디렉터리에 가면 3개의 파일이 생성되어 있다.

각 파일이 설명하는 내용은 문서의 말을 빌리자면 아래와 같다.

BANDWIDTH_REPORT.csv: 레이어별 SRAM과 DRAM에 접근할 때 각 operand에 대한 평균, 최대 대역폭COMPUTE_REPORT.csv: 레이어별 연산과 관련된(e.g compute cycles, stalls, etc) 정보DETAILED_ACCESS_REPORT.csv: 레이어별 SRAM과 DRAM에 대한 접근 횟수에 관련된 정보

여기에는 한 가지 문제가 있는데,

위 세 개 파일은 결과의 summary라는 점이다.

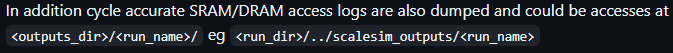

그런데 문서에 의하면 SRAM과 DRAM에 대한 traces도 제공을 한다고 되어있다.

그말인 즉슨, 실행 후 생성될 파일이 더 있다는 것인데..

아무리 찾아봐도 없다.

깃허브의 Issues에서 찾아보니 이에 대한 질문이 2개 정도 있다.

1. "Where is the interface to DRAMsim2? #71" (2023. 8. 2)

이에 대한 메인테이너의 답변은 "기본적으로 ../test_runs에 기록된다."인데,

로그 파일 생성 매개 변수를 전달하지 않으면 저 디렉터리가 생성되고 거기에 결과 파일이 생성되는 것은 맞다.

그런데 traces 파일은 여전히 생성되지 않는다.

2. "How to generate the DRAM trace and energy mentioned in the paper? #80" (2023. 10. 11)

메인테이너의 답변 없이 다음 날 본인 스스로 closed 했다. 뭔가 알아낸 것인가..

향후 access pattern 등을 분석하기 위해 꼭 필요할 것 같으니, 코드 분석할 때 왜 안생기는지 꼼꼼히 살펴봐야겠다.

혹시 원인을 아는 분이 계시다면 댓글로 알려주시면 감사드리겠습니다..!

+) 알아냈습니다.

왜 trace가 생성되지 않았는지 이유가 궁금하다면 아래 글에 가서 확인해보시고,

SCALE-SIM 뜯어보기 (2): 실행 진입점과 scalesim

실행 진입점? 그냥 main(..) 함수라는 의미다. 이 역시 알만한 사람들일테니 명령행 인자가 어떻고, 파이썬은 조건문을 사용해서 어떻게 정의하고 이런 것은 생략한다. 코드 분석은 웬만하면

hwkang4snn.tistory.com

trace 파일을 생성하는 방법만 궁금하다면,

scalesim/scale.py 파일의 34번 줄에 save_disk_space를 False로 바꾸시면 됩니다.

이렇게 SCALE-SIM의 설치와 시뮬레이션, 결과 확인 과정을 간단하게 알아보았다.

다음 포스팅에서는 SCALE-SIM에서 실행 진입점과 클래스 scalesim에 대한 코드를 분석할 것이다.

'HPC > SCALE-SIM' 카테고리의 다른 글

| SCALE-SIM 뜯어보기 (6): single_layer_sim.py (0) | 2024.11.26 |

|---|---|

| SCALE-SIM 뜯어보기 (5): simulator.py (0) | 2024.11.15 |

| SCALE-SIM 뜯어보기 (4): scale_config.py [pt.1] (0) | 2024.11.14 |

| SCALE-SIM 뜯어보기 (3): topology_utils.py [pt.1] (0) | 2024.11.13 |

| SCALE-SIM 뜯어보기 (2): 실행 진입점과 scalesim (0) | 2024.11.12 |